CompactPCI<sup>®</sup> CPN5360 Single Board Computer and Transition Module

### Installation and Reference Guide

CPN5360A/IH1

August 25, 2000 Edition

© Copyright 2000 Motorola, Inc.

All Rights Reserved

Printed in the United States of America

Motorola<sup>®</sup> and the Motorola symbol are registered trademarks of Motorola, Inc. Intel<sup>®</sup> and the Intel logo are registered trademarks of Intel Corporation. Pentium<sup>®</sup> is a registered trademark of Intel Corporation. MMX<sup>™</sup> and the MMX logo are trademarks of Intel Corporation. Windows NT<sup>®</sup> is a registered trademark of Microsoft in the US and other countries CompactPCI<sup>®</sup> is a registered trademark of PCI Industrial Computer Manufacturers Group. Phoenix<sup>®</sup> is a registered trademark of Phoenix Technologies Ltd.

All other products mentioned in this document are trademarks or registered trademarks of their respective holders.

### Notice

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to the Motorola Computer Group website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Motorola, Inc.

It is possible that this publication may contain reference to, or information about Motorola products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

### Limited and Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice applies unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013v (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995)

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

### Safety Summary

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result in personal injury or damage to the equipment.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. If the equipment is supplied with a three-conductor AC power cable, the power cable must be plugged into an approved three-contact electrical outlet, with the grounding wire (green/yellow) reliably connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable must meet International Electrotechnical Commission (IEC) safety standards and local electrical regulatory codes.

#### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in any explosive stmosphere such as in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment could result in an explosion and cause injury or damage.

#### Keep Away From Live Circuits Inside the Equipment.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified service personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Service personnel should not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, such personnel should always disconnect power and discharge circuits before touching components.

#### Use Caution When Exposing or Handling the CRT.

Breakage of a Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, do not handle the CRT and avoid rough handling or jarring of the equipment. Handling of a CRT should be done only by qualified service personnel using approved safety mask and gloves.

#### Do Not Substitute Parts or Modify Equipment.

Do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that safety features are maintained.

#### **Observe Warnings in Manual.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

To prevent serious injury or death from dangerous voltages, use extreme caution when handling, testing, and adjusting this equipment and its components.

### Flammability

All Motorola PWBs (printed wiring boards) are manufactured with a flammability rating of 94V-0 by UL-recognized manufacturers.

### **EMI** Caution

This equipment generates, uses, and can radiate electromagnetic energy. It may cause or be susceptible to electromagnetic interference (EMI) if not installed and used with adequate EMI protection.

### **CE Notice (European Community)**

This is a Class A product. In a domestic environment, this product may cause radio interference, in which case the user may be required to take adequate measures.

Motorola Computer Group products with the CE marking comply with the EMC Directive (89/336/EEC). Compliance with this directive implies conformity to the following European Norms:

EN55022 "Limits and Methods of Measurement of Radio Interference Characteristics of Information Technology Equipment"; this product tested to Equipment Class A

EN50082-1:1997 "Electromagnetic Compatibility--Generic Immunity Standard, Part 1, Residential, Commercial and Light Industry".

System products also fulfill EN60950 (product safety) which is essentially the requirement for the Low Voltage Directive (73/23/EEC).

Board products are tested in a representative system to show compliance with the above mentioned requirements. A proper installation in a CE-marked system will maintain the required EMC/safety performance.

In accordance with European Community directives, a "Declaration of Conformity" has been made and is on file within the European Union. The "Declaration of Conformity" is available on request. Please contact your sales representative.

### **Lithium Battery Caution**

This product contains a lithium battery to power the clock and calendar circuitry.

Danger of explosion if battery is replaced incorrectly. Replace battery only with the same or equivalent type recommended by the equipment manufacturer. Dispose of used batteries according to the manufacturer's instructions.

Il y a danger d'explosion s'il y a remplacement incorrect de la batterie. Remplacer uniquement avec une batterie du même type ou d'un type équivalent recommandé par le constructeur. Mettre au rebut les batteries usagées conformément aux instructions du fabricant.

Explosionsgefahr bei unsachgemäßem Austausch der Batterie. Ersatz nur durch denselben oder einen vom Hersteller empfohlenen Typ. Entsorgung gebrauchter Batterien nach Angaben des Herstellers.

#### CHAPTER 1 CPN5360 Single Board Computer and Transition Module Overview

| Introduction            | 1-1 |

|-------------------------|-----|

| Additional Features     | 1-1 |

| Input/Output Interfaces | 1-2 |

| Special Functions       |     |

#### CHAPTER 2 Getting Started

| Antistatic Precautions                                     | 2-1 |

|------------------------------------------------------------|-----|

| Before Installing the CPN5360                              | 2-2 |

| Installing the CPN5360                                     | 2-2 |

| Powering up the CPN5360                                    |     |

| Replacing Lithium Batteries                                |     |

| Front Panel Connectors and Indicators on the CPN5360       |     |

| Rear Panel Connectors on the CPN5360TM80 Transition Module |     |

| Rear Panel Connectors on the CPN53601M80 Transition Module | 2-9 |

#### CHAPTER 3 Components on the CPN5360

| Components on the CPN5360 Single Board Computer | 3-1 |

|-------------------------------------------------|-----|

| Components on the CPN5360TM80 Transition Module |     |

| Connecting to Board Connectors                  | 3-6 |

| CPU Speed Settings                              | 3-7 |

#### CHAPTER 4 Functional Description

| Introduction                                                | 4-1 |

|-------------------------------------------------------------|-----|

| PhoenixBIOS Description                                     | 4-1 |

| Soft Reset                                                  | 4-1 |

| Headless Operation                                          |     |

| Remote Setup                                                | 4-2 |

| Network Boot                                                |     |

| Peripheral Component Interconnect (PCI) Local Bus Interface |     |

| PCI Mezzanine Card Limitations                              | 4-3 |

| CompactPCI Bus Interface                                    |     |

| Using the CPN5360 in a Non-Host Slot                        | 4-4 |

|                                                             |     |

| Peripheral Reset Function                                 |  |

|-----------------------------------------------------------|--|

| Peripheral PCI Interrupt Function                         |  |

| Peripheral PCI Clock Function                             |  |

| Peripheral Hot Swap Function                              |  |

| Using the CPN5360 in a Host Slot                          |  |

| Host Reset Function                                       |  |

| Host PCI Interrupt Function                               |  |

| Host PCI Clock Function                                   |  |

| Host Hot Swap Function                                    |  |

| Watchdog Timer                                            |  |

| Memory Address Mapping                                    |  |

| I/O Address Map                                           |  |

| Field Programmable Gate Array Registers                   |  |

| FPGA Register Descriptions                                |  |

| Status Register                                           |  |

| EEPROM Control Register                                   |  |

| Watchdog Timer Register                                   |  |

| Interrupt Select Register                                 |  |

| SCI Enable Register                                       |  |

| NMI Enable Register                                       |  |

| IRQ Enable Register                                       |  |

| Alarm Enable Register                                     |  |

| Latch Enable Register                                     |  |

| Power-On Flag Register                                    |  |

| LAN A Control Register                                    |  |

| LAN B Control Register                                    |  |

| Flash BIOS Write Protect Control Register                 |  |

| Slot Control Port Register                                |  |

| Jump to User Code in Alternate Flash Bank                 |  |

| DEC21554 PCI-to-PCI Bridge Configuration                  |  |

| Setup Option Number 1 - "BIOS Setup of DEC21554 Bridge"   |  |

| Setup Options 2, 3, 4, and 5                              |  |

| Sample Code for Accessing a Field Programmable Gate Array |  |

### CHAPTER 5 Connector Pin Assignments

| Ethernet Connectors                                   |     |

|-------------------------------------------------------|-----|

| Serial Port Connectors                                |     |

| Video Connector for the CPN5360TM80 Transition Module |     |

| Keyboard/Mouse P/S2 Connector for the CPN5360TM80     |     |

| Transition Module                                     | 5-6 |

| Keyboard/Mouse/Power LED Connector for the CPN5360TM80              |      |

|---------------------------------------------------------------------|------|

| Transition Module                                                   | 5-6  |

| USB Connectors for the CPN5360TM80 Transition Module                | 5-7  |

| Parallel Connector for the CPN5360TM80 Transition Module            | 5-8  |

| EIDE Connector for the CPN 5360TM80 Transition Module               | 5-9  |

| CompactFlash Connector for the CPN5360TM80 Transition Module        | 5-10 |

| Floppy Connector for the CPN5360TM80 Transition Module              | 5-12 |

| Indicator LED/Miscellaneous Connector for the CPN5360TM80           |      |

| Transition Module                                                   | 5-14 |

| CPN5360 Single Board Computer, CompactPCI Bus                       |      |

| Connectors (J1 and J2)                                              | 5-15 |

| CPN5360 Single Board Computer, CompactPCI Rear I/O                  |      |

| Connectors (J3, J4, and J5)                                         | 5-17 |

| CPN5360TM80 Transition Module, Rear I/O Connectors (J3, J4, and J5) | 5-25 |

#### APPENDIX A Specifications

### APPENDIX B Windows NT 4.0 Installation Error

#### APPENDIX C Related Documentation

| Motorola Computer Group Documents | . C- | 1 |

|-----------------------------------|------|---|

| URLs                              | . C- | 1 |

| Figure 1-1. Block Diagram of the CPN5360 Single Board Computer          | 1-4  |

|-------------------------------------------------------------------------|------|

| Figure 2-1. Installing the CPN5360 Single Board Computer and Transition |      |

| Module in Your Computer Chassis                                         | 2-3  |

| Figure 2-2. Front Panel Connectors and LEDs on the CPN5360 Single       |      |

| Board Computer                                                          | 2-8  |

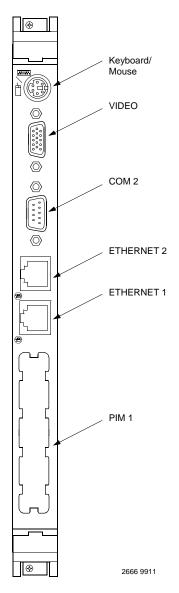

| Figure 2-3. Rear Panel Connectors on the CPN5360 Transition Module      | 2-10 |

| Figure 3-1. Location of Major Components on the CPN5360 Single          |      |

| Board Computer                                                          | 3-2  |

| Figure 3-2. Major Components on the CPN5360TM80 Transition Module       | 3-5  |

| Table 1-1. Input/Output Interfaces on the CPN5360 Single Board Computer and        |   |

|------------------------------------------------------------------------------------|---|

| the CPN5360TM80 Transition Module1-3                                               | 3 |

| Table 3-1. List of Front Panel Connectors, Board Connectors and Components         |   |

| for the CPN5360 Single Board Computer                                              | 3 |

| Table 3-2. List of Front Panel Connectors, Board Connectors and Components         |   |

| for the CPN5360TM80 Transition Module                                              | 5 |

| Table 4-1. Memory Addresses and Descriptions    4-9                                | ) |

| Table 4-2. I/O Addresses and Descriptions                                          | ) |

| Table 4-3. System Management Modes                                                 | 3 |

| Table 4-4. Index and data register address and function                            | 3 |

| Table 4-5. Map of the FPGA register set                                            | 1 |

| Table 4-6. Bit descriptions for the STAT register                                  | 1 |

| Table 4-7. Bit descriptions for the ECTRL register                                 |   |

| Table 4-8. Bit descriptions for the Watchdog Timer register                        | 5 |

| Table 4-9. Bit values for selecting watchdog timeout time4-17                      | 7 |

| Table 4-10. Bit values defining watchdog timeout and disabling4-18                 | 3 |

| Table 4-11. SOFT_RST bit 5 settings4-18                                            | 3 |

| Table 4-12. Bit descriptions for the INTUM register                                | ) |

| Table 4-13. Bit values for determining driven IRQ lines                            | ) |

| Table 4-14. Bit descriptions for the SCIEN register                                | l |

| Table 4-15. Bit descriptions for the NMIEN register                                | 2 |

| Table 4-16. Bit descriptions for the IRQEN register    4-23                        | 3 |

| Table 4-17. Bit descriptions for the ALEN register    4-24                         | 1 |

| Table 4-18. Bit descriptions for the LEN register    4-25                          | 5 |

| Table 4-19. Bit descriptions for the Power-On Flag register                        | 7 |

| Table 4-20. Bit descriptions for the LAN A register                                | 3 |

| Table 4-21. Bit descriptions for the LAN B register                                | ) |

| Table 4-22. Bit descriptions for the Flash BIOS Write Protect Control register4-30 | ) |

| Table 4-23. Bit selections for the Flash BIOS Device Bank Control                  | ) |

| Table 4-24. Bit descriptions for the Slot Control Port register                    | l |

| Table 4-25. Sample Code for Programming a Field Programmable Gate Array4-34        | 1 |

| Table 5-1. Ethernet Connector Pin Assignments for the CPN5360 Single Board         |   |

| Computer and CPN5360TM80 Transition Module5-1                                      | 1 |

| Table 5-2. Serial Port Connector Pin Assignments for the CPN5360 Single Board |       |

|-------------------------------------------------------------------------------|-------|

| Computer (RJ-45) (J18)                                                        | . 5-2 |

| Table 5-3. Serial Port Connector Pin Assignments for the CPN5360TM80          |       |

| Transition Module (COM2) (J28)                                                | . 5-3 |

| Table 5-4. Serial Port Connector Pin Assignments for the CPN5360TM80          |       |

| Transition Module (COM1) (J21)                                                | . 5-4 |

| Table 5-5. Video Connector Pin Assignments for the CPN5360TM80 Transition     |       |

| Module (J16)                                                                  | . 5-5 |

| Table 5-6. Keyboard/Mouse P/S2 Connector Pin Assignments for the              |       |

| CPN5360TM80 Transition Module                                                 | . 5-6 |

| Table 5-7. Keyboard/Mouse/Power LED Connector Pin Assignments for the         |       |

| CPN5360TM80 Transition Module                                                 | . 5-6 |

| Table 5-8. USB Connector Pin Assignments for the CPN5360TM80 Transition       |       |

| Module                                                                        | . 5-7 |

| Table 5-9. Parallel Connector Pin Assignments for the CPN5360TM80             |       |

| Transition Module                                                             | . 5-8 |

| Table 5-10. EIDE Connector Pin Assignments for the CPN5360TM80 Transition     |       |

| Module                                                                        | . 5-9 |

| Table 5-11. CompactFlash Connector Pin Assignments for the CPN5360TM          |       |

| Transition Module                                                             | 5-10  |

| Table 5-12. Floppy Connector Pin Assignments for the CPN5360TM80              |       |

| Transition Module                                                             | 5-12  |

| Table 5-13. Indicator LED/Miscellaneous Connector Pin Assignments for the     |       |

| CPN5360TM80 Transition Module (J2)                                            | 5-14  |

| Table 5-14. CPN5360 Backplane Connector Pin Assignments (J1)                  | 5-15  |

| Table 5-15. CPN5360 Backplane Connector Pin Assignments (J2)                  | 5-16  |

| Table 5-16. CPN5360 Single Board Computer, Rear I/O Connector Pin             |       |

| Assignments (J3)                                                              | 5-17  |

| Table 5-17. Signal Descriptions for the CPN5360 Single Board Computer         |       |

| Backplane Connector (J3)                                                      | 5-18  |

| Table 5-18. CPN5360 Rear I/O Pin Assignments (J4)                             | 5-19  |

| Table 5-19. Signal Descriptions for the CPN5360 Single Board Computer         |       |

| Backplane Connector (J4)                                                      | 5-20  |

| Table 5-20. CPN5360 Rear I/O Pin Assignments (J5)                             | 5-22  |

| Table 5-21. Signal Descriptions for the CPN5360 Single Board Computer         |       |

| Backplane Connector (J5)                                                      | 5-23  |

| Table 5-22. CPN5360TM80 Transition Module, Rear I/O Connector Pin             |       |

| Assignments (J3)                                                              | 5-25  |

| Table 5-23. Signal Descriptions for the CPN5360TM80 Transition Module,      |

|-----------------------------------------------------------------------------|

| Backplane Connector (J3)                                                    |

| Table 5-24. CPN5360TM80 Transition Module, Rear I/O Connector               |

| Pin Assignments (J4)                                                        |

| Table 5-25. Signal Descriptions for the CPN5360TM80 Transition Module,      |

| Backplane Connector (J4)                                                    |

| Table 5-26. CPN5360TM80 Transition Module, Rear I/O Connector               |

| Pin Assignments (J5)                                                        |

| Table 5-27. Signal Descriptions for the CPN5360TM80 Transition Module,      |

| Backplane Connector (J5)                                                    |

| Table A-1. Power Requirements for the CPN5360 Single Board Computer and     |

| Transition Module                                                           |

| Table A-2. Physical Characteristics of the CPN5360 Single Board ComputerA-1 |

| Table A-3. Lithium Battery Specifications                                   |

| Table A-4. Environmental Specifications                                     |

| Table C-1. Motorola Computer Group Documents                                |

## **About This Manual**

This CompactPCI<sup>®</sup> CPN5360 Single Board Computer (SBC) Installation and Reference Guide describes the installation, components, and configurations of the CPN5360 SBC and Transition Module. Use this guide for general and technical information about the CPN5360 CompactPCI System CPU.

| Model<br>Numbers | Description                                                                                                                                      |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CPN5360-266      | CompactPCI Single Board Computer with 266 MHz processor and 128 or 256MB SDRAM                                                                   |  |

| CPN5360-333      | CompactPCI Single Board Computer with 333 MHz<br>processor and 128 or 256MB SDRAM with or<br>without hard drive and J4 connector                 |  |

| CPN5360-500      | CompactPCI Single Board Computer with 500MHz<br>processor and 128 or 256MB SDRAM with or<br>without hard drive and J4 connector                  |  |

| CPN5360TM        | CompactPCI Transition Module with one or two<br>PIM sites, key/board mouse, USB, CompactFlash,<br>EIDE, floppy, serial, parallel Ethernet, video |  |

### **Summary of Changes**

This table summarizes revisions to this manual.

| Date:           | Change:                                                                                                                         |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| August 25, 2000 | Added section, "About this Manual."                                                                                             |  |  |

|                 | Revised Chapter 1, for CPN5360 models for use with H.110 bus.                                                                   |  |  |

|                 | Revised Table 1-1, for floppy access information on the CPN5360 and CPN5360T.                                                   |  |  |

|                 | Removed "System Management Bus (SMBUS) Alert<br>Signal" from "Special Functions", "Advanced System<br>Monitoring" in Chapter 1. |  |  |

|                 | Revised "Remote Setup" in Chapter 4.                                                                                            |  |  |

|                 | Added "PCI Mezzanine Card Limitations" in Chapter 4.                                                                            |  |  |

|                 | Added note to "Using the CPN5360 in a Host Slot" section in Chapter 4.                                                          |  |  |

|                 | Revised Table 4-5, under "Device 00h System" to 00 Status.                                                                      |  |  |

|                 | Revised Table A-1, Appendix A.                                                                                                  |  |  |

|                 | Added cooling specification to Table A-4, Appendix A.                                                                           |  |  |

|                 | Revised temperature specifications for "Operating" and "Non-operating" conditions in, Table A-4, Appendix A.                    |  |  |

### **Overview of Contents**

This Chapter or Appendix: Gives you: Chapter 1, "CPN5360 Single a detailed CPN5360 product description, Board Computer and Transition information about input/output interfaces, a Module Overview" CPN5360 SBC block diagram and information about special functions. Chapter 2, "Getting Started" information about ESD, board installation and power up, replacement of lithium batteries, locations of connectors and indicators. Chapter 3, "Components on the the location of major components on the CPN5360 CPN5360" SBC and CPN5360TM80 Transition Module. Chapter 4, "Functional a functional description including information about Description" the PCI Bus, host and non-host slot mounting, the watchdog timer, memory address mapping, the I/O address map and the FPGA registers. Chapter 5, "Pin Assignments" pin assignments for the SBC and transition module Appendix A, "Specifications" board specifications Appendix B, "WindowsNT 4.0 information about a potential error in the event Installation Error" viewer log during WindowsNT 4.0 installation Appendix C, "Related information about related Motorola Computer Documentation" Group documents, other related documents and URLs for access to more information.

This section contains a short description of the content of each chapter and appendix in this manual.

### Who Should Use This Guide

The information in this guide is written for system installers, original equipment manufacturers (OEM) and technicians. The procedures assume familiarity with the safety practices and regulatory compliance required for using and modifying electronic equipment. Personnel who install CompactPCI systems should be trained and experienced with the installation of computers and computer equipment.

### **Comments and Suggestions**

We welcome and appreciate your comments on our documentation. We want to know what you think about our manuals and how we can make them better. Mail comments to:

> Motorola Computer Group Reader Comments DW164 2900 S. Diablo Way Tempe, Arizona 85282

You can also submit comments to the following e-mail address: reader-comments@mcg.mot.com

In all your correspondence, please list your name, position, and company. Be sure to include the title and part number of the manual and tell how you used it. Then tell us your feelings about its strengths and weaknesses and any recommendations for improvements.

# CPN5360 Single Board Computer and Transition Module Overview

1

### Introduction

The CPN5360 Single Board Computer (SBC) is a hot swap, single-slot, CompactPCI<sup>®</sup> (Compact Peripheral Communication Interface) compliant computer. It is powered by a Pentium<sup>®</sup> II processor Low Power module. It can serve either as a standard CompactPCI peripheral CPU or as a system controller. Some models of the CPN5360 SBC work in H.110 systems. These models are the same as other versions except that the J4 connector is removed.

The highly integrated processor gives you a 16MB on-board solid-state disk, USB, PCI EIDE, accelerated graphics, dual Fast Ethernet controllers, and standard PC I/O plus two PMC sites for additional expansion.

An optional Transition Module gives you backplane I/O for PMC sites and on-board devices.

The CPN5360 meets the needs of embedded application developers. Typical applications include broadband data or intelligent network switching, CTI server, industrial control and automation, military and aerospace, and medical, scientific, or imaging products.

### **Additional Features**

The CPN5360 gives you these features:

- Pentium II processor Low Power module for high end embedded applications

- □ Up to 256MB on-board 3.3V SDRAM memory

- □ Accelerated 2D graphics with 2MB video memory

- Dual Fast Ethernet controllers for monitoring and telecom applications

- Hot Swap compatibility allowing insertion or removal of the CPN5360 and other peripheral CPU slot boards while the chassis is powered up

- □ An array of on-board I/O available from the front panel of the CPN5360 and/or the rear panel via the CPN5360TM80 Transition Module

- □ Models available for H.110 interface

The CPN5360TM80 Transition Module gives you these features:

- $\Box$  rear panel connections for:

- PS/2 keyboard/mouse

- video

- COM2 (serial port)

- Ethernet 1 and 2

- PIM 1

- □ on-board connectors for:

- PS/2 keyboard/mouse

- floppy

- USB0 and USB1

- primary and secondary IDE

### **Input/Output Interfaces**

Refer to Table 1-1 for brief descriptions of the input/output interfaces on the CPN5360 Single Board Computer and CPN5360TM80 Transition Module. Do not use the rear panel connectors and internal connectors at the same time.

**Note** When the identical function is available through the CPN5360's front panel and the rear transition module, you can use either the front or the rear, **not both.**

#### Table 1-1. Input/Output Interfaces on the CPN5360 Single Board Computer and the CPN5360TM80 Transition Module

| Function             | CPN5360      |          | CPN5360TM80 Transition<br>Module |                                    |

|----------------------|--------------|----------|----------------------------------|------------------------------------|

|                      | Front Panel  | On-board | Rear Panel                       | On-board                           |

| Ethernet 1           | RJ-45        | -        | RJ-45                            | -                                  |

| Ethernet 2           | -            | -        | RJ-45                            | -                                  |

| COM1 (Serial Port 1) | RJ-45        | -        | -                                | 10-pin shrouded                    |

| COM2 (Serial Port 2) | -            | -        | 9-pin D-sub                      | -                                  |

| PMC Panel            | PMC 1 Device | -        | PMC 1 Device                     | -                                  |

| PMC Panel            | PMC 2 Device | -        | -                                | -                                  |

| Keyboard/Mouse       | -            | -        | 6-pin mini-DIN                   | 12-pin connector                   |

| Floppy <sup>1</sup>  | -            | -        | -                                | 34-pin connector                   |

| Parallel             | -            | -        | -                                | 26-pin shrouded                    |

| USB 0 and USB 1      | -            | -        | -                                | two - stacked 4-<br>pin connectors |

| Video                | -            | -        | 15-pin D-sub                     | -                                  |

| Primary IDE          | -            | -        | -                                | 40-pin connector                   |

| Secondary IDE        | -            | -        | -                                | 40-pin connector                   |

| CompactFlash         | -            | -        | -                                | 50-pin connector                   |

<sup>1</sup> The CPN5360 Single Board Computer does not offer front panel or on-board access to a floppy connector. The floppy interface routes through the J4 connector on the CPN5360. This connector is not on telephony (T) versions of the board. Driver updates on the CPN5360T must be done over the network.

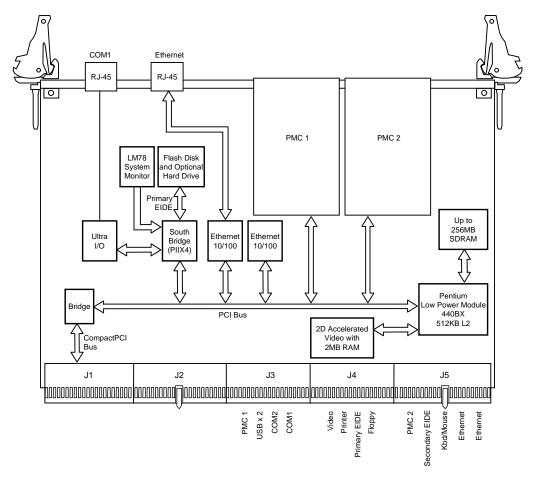

Refer to Figure 1-1 for a block diagram of the CPN5360 Single Board Computer.

Figure 1-1. Block Diagram of the CPN5360 Single Board Computer

### **Special Functions**

The CPN5360 uses these functions designed for use in certain applications. Refer to Chapter 4 for programmer's reference information.

Watchdog Timer

The watchdog timer can operate in four modes:

- Disabled

- Sets the timeout flag in the Watchdog Strobe/Status port in ISA I/O memory map

- Sets the timeout flag in the Watchdog Strobe/Status port in ISA I/O memory map + Assert a selectable interrupt (ISA IRQ)

- Sets the timeout flag in the Watchdog Strobe/Status port in ISA I/O memory map + Assert NMI followed by a system Reset or Soft Reset

You can program the watchdog timer via registers in the ISA I/O memory map. The watchdog timer is protected from being accidentally enabled. The timer supports a range of count down time-outs up to eight minutes.

□ Advanced System Monitoring

The CPN5360 monitors the following system events:

- On-card temperature

- MMC2 thermal fault

- On-card voltages +5V, +3.3V, +/-12V and the processor core voltage

- Chassis power supply loss of regulation

1

1

# Getting Started

2

This chapter gives you:

- basic installation information for the CPN5360 Single Board Computer (SBC) and Transition Module

- □ information about lithium battery replacement

- □ information about front and rear panel connectors on the SBC and transition module

- **Note** This document treats the CPN5360 SBC as a component of a system, and assumes that you install it in a CompactPCI backplane that is PICMG compliant.

### **Antistatic Precautions**

Wrist Strap

Motorola strongly recommends that you use an antistatic wrist strap and a conductive foam pad when installing or upgrading a system. Electronic components, such as disk drives, computer boards, and memory modules, can be extremely sensitive to electrostatic discharge (ESD). After removing the component from its protective wrapper or from the system, place the component flat on a grounded, static-free surface (and, in the case of a board, component side up). Do not slide the component over any surface.

If an ESD station is not available, you can avoid damage resulting from ESD by wearing an antistatic wrist strap (available at electronics stores) that is attached to an active electrical ground. Note that a system chassis may not be grounded if it is unplugged.

2

### Before Installing the CPN5360

After removing the CPN5360 from its packaging:

- □ Check for obvious physical damage.

- □ Verify that the coin cell battery is in its holder and inserted correctly.

Make sure that you disconnect the chassis from the main power supply before you continue.

### Installing the CPN5360

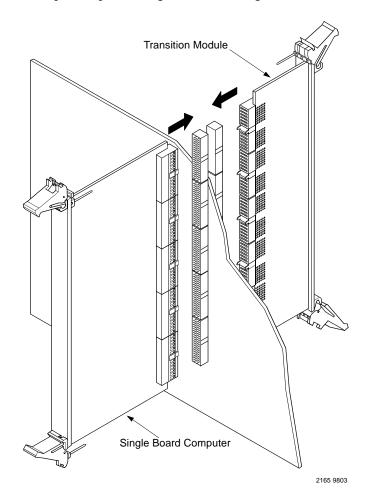

Use these steps to install the CPN5360 into your computer chassis. Refer to Figure 2-1.

- 1. Follow the instructions in your chassis user manual to remove any outer cover.

- 2. Locate the desired peripheral slot.

- 3. Remove any filler panel (or existing board) that might fill that slot.

- 4. Install the top and bottom edge of the CPN5360 in the guides of the chassis.

- 5. Ensure that the levers of the two injector/ejectors are in the inward position.

- 6. Slide the CPN5360 into the chassis until resistance is felt.

- 7. Simultaneously move the injector/ejector levers in an outward direction.

- Verify that the CPN5360 is properly seated and secure it to the chassis using the two screws located adjacent to the injector/ejector levers.

- 9. Connect the appropriate cables to the CPN5360.

10. Repeat steps 3 through 9 for installing the transition module.

Figure 2-1. Installing the CPN5360 Single Board Computer and Transition Module in Your Computer Chassis

### Powering up the CPN5360

When you are ready to power up the CPN5360:

- Verify that the chassis power supply voltage setting matches the voltage present in the country of use (if the power supply in your system is not auto-sensing).

- □ On powering up, the CPN5360 displays the PhoenixBIOS banner and then runs a memory test.

### **Replacing Lithium Batteries**

Follow these safety rules for proper battery operation and to reduce equipment and personal injury hazards when handling lithium batteries. Use the battery for its intended application only.

**Note Do not** recharge, open, puncture or crush, incinerate, expose to high temperatures or dispose of in your general trash collection.

To replace the lithium battery, observe the following guidelines and follow the steps below.

**Note** When replacing the battery, you must apply power to the board to prevent data loss.

To prevent serious injury or death from dangerous voltages, use extreme caution when handling, testing, and adjusting this equipment and its components.

Lithium batteries incorporate flammable materials such as lithium and organic solvents. If lithium batteries are short-circuited or exposed to high temperature or pressure, they may burst open and ignite, possibly resulting in injury and/or fire. When dealing with lithium batteries, carefully follow the precautions listed below to prevent accidents.

- Do not short-circuit.

- □ Do not disassemble, deform or apply excessive pressure.

- Do not heat or incinerate.

- Do not apply solder directly.

- Do not use different models, or new and old batteries together.

- Do not charge.

- □ Always check proper polarity.

To replace the on-board backup battery, follow the steps below.

Danger of explosion if battery is replaced incorrectly.

Replace only with the same or equivalent type recommended by the equipment manufacturer. Dispose of used batteries according to the manufacturer's instructions.

Avoid touching areas of integrated circuitry; static discharge can damage circuits.

Use ESD

Attach an ESD strap to your wrist. Attach the other end of the ESD strap to an electrical ground. (Note that the system chassis may not be grounded if it is unplugged.) Secure the ESD strap to your wrist and to ground throughout the procedure.

Wrist Strap

- 1. To remove the battery from the module, carefully pull the battery from the socket.

- 2. Before installing a new battery, make sure that the battery pins are clean.

- 3. Not the battery polarity and press the new battery into the socket.

- **Note** No soldering is required when the battery is in the socket.

- 4. Recycle or dispose of the old battery according to local regulations and manufacturer's instructions.

Computer Group Literature Center Web Site

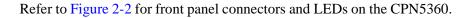

# Front Panel Connectors and Indicators on the CPN5360

The CPN5360's front panel has connectors for:

- □ Ethernet 1 (RJ-45)

- □ COM1 serial port (RJ-45)

- □ two PMC Panels (PMC1 and PMC2)

LED Indicator lights on the front panel display of the CPN5360 include:

- □ Hot Swap status (Blue LED)

- □ Power (Green LED)

2

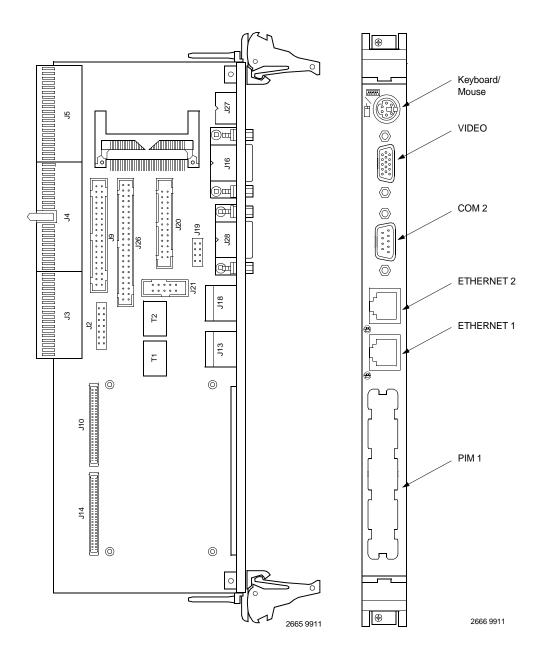

#### Figure 2-2. Front Panel Connectors and LEDs on the CPN5360 Single Board Computer

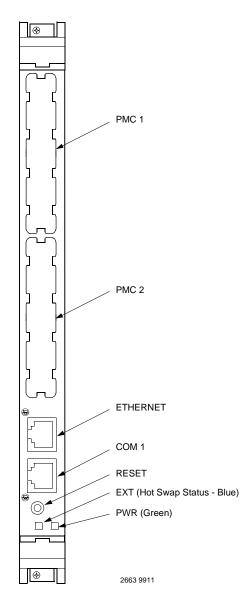

### Rear Panel Connectors on the CPN5360TM80 Transition Module

The CPN5360 Transition Module has connectors on the rear panel for:

- □ keyboard/mouse (PS/2)

- □ Ethernet 1 and Ethernet 2 (RJ45)

- □ COM2 (serial port) (9 pin D-sub)

- □ video (15 pin high density D-sub)

# Components on the CPN5360 Single Board Computer

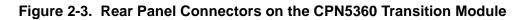

The CPN5360 Single Board Computer (SBC) carries components on both sides. Figure 3-1 shows the location of the on-board connectors. There are no on-board jumpers.

#### Figure 3-1. Location of Major Components on the CPN5360 Single Board Computer

Table 3-1 lists the connectors available to support devices on the CPN5360. Refer to Figure 3-1. Refer to Chapter 5 for connector pin assignment.

## Table 3-1. List of Front Panel Connectors, Board Connectors and<br/>Components for the CPN5360 Single Board Computer

| Connector | Description                                |

|-----------|--------------------------------------------|

| J1        | CompactPCI Bus Connector                   |

| J2        | CompactPCI Bus Connector                   |

| J3        | Rear I/O CompactPCI Connector              |

| J4        | Rear I/O CompactPCI Connector              |

| J5        | Rear I/O CompactPCI Connector              |

| J6        | Debug Port                                 |

| J10       | PMC2 bus signal connector                  |

| J11       | PMC1 bus signal connector                  |

| J12       | PMC2 I/O connector                         |

| J13       | PMC1 I/O connector                         |

| J14       | PMC2 bus signal connector                  |

| J15       | PMC1 bus signal connector                  |

| J16       | PCI 64 bit PCI extension on PMC2 connector |

| J17       | PCI 64 bit PCI extension on PMC1 connector |

| J18       | COM1 (serial port - RJ45 connector)        |

| J21       | Ethernet connector (RJ-45)                 |

# Components on the CPN5360TM80 Transition Module

Figure 3-2 shows major components on the CPN5360TM80 Transition Module.

Figure 3-2. Major Components on the CPN5360TM80 Transition Module

3

Table 3-2 lists the connectors available to support devices on the CPN5360TM80 Transition Module. Refer to Figure 3-2. Refer to Chapter 5 for connector pin assignment.

| Connector | Description                   |

|-----------|-------------------------------|

| J2        | Drive LED's, Reset            |

| J3        | Rear I/O CompactPCI Connector |

| J4        | Rear I/O CompactPCI Connector |

| J5        | Rear I/O CompactPCI Connector |

| J6        | Keyboard/Mouse (internal)     |

| J9        | Floppy                        |

| J10       | PIM connector (PMC I/O)       |

| J13       | Ethernet 1                    |

| J14       | PIM connector (PMC I/O)       |

| J15       | PIM connector (PMC I/O)       |

| J16       | Video                         |

| J18       | Ethernet 2                    |

| J19       | USB connector                 |

| J20       | Parallel connector            |

| J21       | COM1 (serial port 1)          |

| J26       | IDE (secondary)               |

| J27       | Keyboard/Mouse (external)     |

| J28       | COM2 (serial port 2)          |

#### Table 3-2. List of Front Panel Connectors, Board Connectors and Components for the CPN5360TM80 Transition Module

## **Connecting to Board Connectors**

The CPN5360 Single Board Computer (SBC) and CPN5360TM80 Transition Module (TM) give you board connectors for attaching peripheral devices. Before installing the CPN5360 SBC or TM, you may want to connect your peripheral cables to the connectors. Refer to Chapter 5, *Connector Pin Assignments* for pin assignment information. **Note** When the identical function is available through the CPN5360 SBC (front panel) and TM (rear panel), you can use either the front or the rear, not both.

Always remove power from the system before connecting peripherals to the CPN5360 SBC or TM. To reduce the risk of personal injury, disconnect the power cord from the power source. Only qualified, experienced electronics personnel should access the interior of a chassis.

The components of the CPN5360 SBC and TM are sensitive to static discharge. While out of the unit, place the modules on a static-dissipative surface or into a static-shielding bag.

## **CPU Speed Settings**

You cannot configure the CPU speed settings.

## **Functional Description**

## Introduction

This chapter gives you information about:

- □ the Peripheral Component Interconnect (PCI) Bus

- $\hfill\square$  host and non-host slot mounting

- □ the watchdog timer

- □ memory address mapping

- □ the I/O address map

- □ Field Programmable Gate Array (FPGA) registers

The CPN5360 BIOS is similar to the CPV5350 BIOS. Refer to *Related Documentation*, Table C-1 for information about how to access the "CPV5350 CompactPCI BIOS and Programmer's Reference Guide" (Motorola part number CPV5350A/PGx). Refer to *Jump to User Code in Alternate Flash Bank* on page 4-32 and *DEC21554 PCI-to-PCI Bridge Configuration* on page 4-32 for more information about the CPN5360 BIOS.

## **PhoenixBIOS Description**

The CPN5360 uses the PhoenixBIOS to provide initial hardware configuration for local devices and local operating system boot.

#### Soft Reset

You can generate a "soft reset" from your keyboard, the watchdog timer, or the front panel push button in Soft Reset Mode. The BIOS preserves as much of the system memory state as possible.

A CPN5360 circuit monitors system power and provides the PWROK signal to the PIIX4E. The PIIX4E distributes the reset to the rest of the board by generating the CPU, PCI, and IDE resets. You can also reset the board using the front panel reset switch and the FPGA watchdog timer. You can program the Watchdog Timer and the front panel push button switch to generate a soft reset. Refer to *Field Programmable Gate Array Registers* on page 4-12 for programming information.

#### **Headless Operation**

The BIOS can operate with no keyboard or display. You do, however, need a keyboard and display to change setup options unless you use the remote setup feature.

#### **Remote Setup**

You can change setup options remotely through the BIOS Setup -Advanced Menu using the RJ45, COM1 port on the front panel of the CPN5360 Single Board Computer. The default settings for a serial console are 9600 baud, 1 stop bit, no parity, and no flow control.

#### **Network Boot**

We include the Intel PXE (Pre-boot Execution Environment) 82559 BIOS extension module to provide operating system boot via one of the 82559 ports. This module is built into the BIOS. You can enable the PXE for either port through the BIOS Setup-Advanced-PCI Configuration Menu.

## Peripheral Component Interconnect (PCI) Local Bus Interface

The PCI local bus is a high-performance, 32-bit bus with multiplexed address and data lines. Use it as an interconnect mechanism between highly-integrated peripheral controller components, peripheral add-in boards and processor/memory systems.

The CPN5360 supports a 32-bit local PCI bus interface. On-board devices connect directly to the local PCI bus.

### **PCI Mezzanine Card Limitations**

The CPN5360 Single Board Computer drives the Peripheral Component Interconnect (PCI) Mezzanine Card's (PMC) PCI Bus to 3.3V logic levels.

Driving the PCI bus to 5V logic levels could damage the PCI devices on the CPN5360.

PMCs used on the CPN5360 must support 3.3V or universal voltage PCI signaling. The CPN5360 is keyed to prevent installation of 5V PMCs.

## **CompactPCI Bus Interface**

The CPN5360 supports a single 64-bit CompactPCI bus interface. You can insert the physical connector into a 64-bit High Availability CompactPCI backplane and make connection to off card CompactPCI peripherals through the PCI-PCI bridge.

## Using the CPN5360 in a Non-Host Slot

The CPN5360 is intended for mounting in a non-host slot as a peripheral CPU. The module configures itself for peripheral mode when it plugs into a peripheral slot. The CompactPCI interface device is a non-transparent bridge (21554). The local CPU enumerates the local devices and sets up the bridge for configuration by the host CPU. The peripheral CPU can also configure itself onto the Compact PCI bus using a scheme allowing it to map itself to a particular area using the geographical addressing CPCI lines. You can read these lines through the FPGA. Refer to the FPGA register description for information about reading these bits.

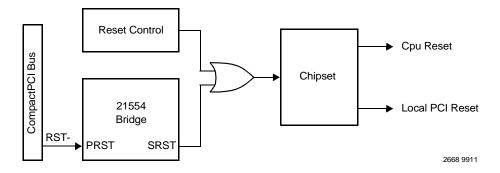

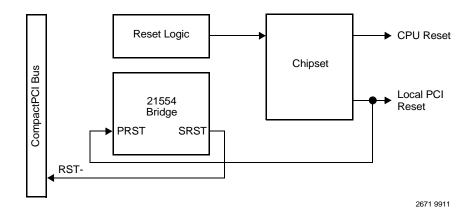

#### **Peripheral Reset Function**

In peripheral mode the PCI reset signal comes from the CompactPCI bus through the bridge to reset all on-card functions. You can reset the card independently without affecting other cards in the system.

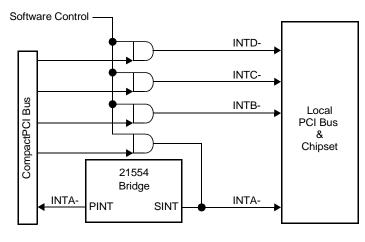

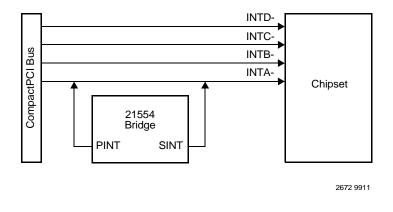

#### **Peripheral PCI Interrupt Function**

In peripheral mode the PCI interrupts route as shown below. The 21554 bridges primary interface can generate a system interrupt via the INTAline on the CompactPCI bus. Local and host CPUs can generate an interrupt to the other CPU via the 21554's primary and secondary doorbell interrupts.

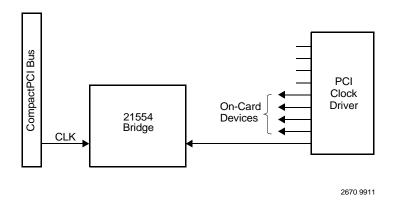

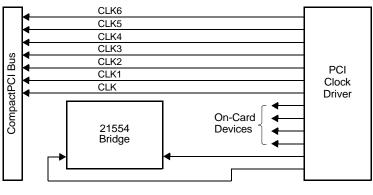

#### **Peripheral PCI Clock Function**

In peripheral mode the 21554's primary interface connects to the CompactPCI CLK (clock) signal. The secondary interface connects to an on-card PCI clock. In this configuration the bridge operates in asynchronous clocking mode.

#### **Peripheral Hot Swap Function**

The CPN5360 complies with the CompactPCI Hot Swap Specification in peripheral mode. You must, however, use a compliant backplane with proper pin staging.

## Using the CPN5360 in a Host Slot

The CPN5360 automatically provides host hardware functions (clocks and REQ/GNT arbitration) when plugged into the host slot. Bus configuration, however, is non-standard. This means you need special software drivers. Also, the BIOS does not support configuration past the bridge. You can read the SYSEN- CPCI line indicating the host mode through the FPGA. Refer to the FPGA register descriptions for information about how to read this bit.

**Note** The CPN5360 is designed mainly for use as a peripheral. The system may need additional CompactPCI bus termination and special software drivers if it is used as a host.

#### **Host Reset Function**

In host mode the on-board reset logic generates the reset. The PCI reset signal routes through the PCI bridge to the CompactPCI bus to reset the system.

#### **Host PCI Interrupt Function**

In host mode the PCI interrupts route as shown below. The on-card PCI interrupts connect to the CompactPCI bus in the standard way.

## **Host PCI Clock Function**

In host mode all seven CompactPCI clock signals provide clocking for all peripheral slots.

#### **Host Hot Swap Function**

Host mode does not support the Hot Swap function. Bus arbitration and clock signals are lost if the board is removed. You can, however, remove the board under power without damage from a Hot Swap compliant backplane slot with proper pin staging.

## Watchdog Timer

The Field Programmable Gate Array (FPGA) includes a watchdog timer. The watchdog timer has four modes of operation:

- 1. disabled

- 2. sets the timeout flag in the Watchdog Strobe/Status port in ISA I/O memory map

- 3. item 2 + assert a selectable interrupt (ISA IRQ)

- 4. item 2 + assert NMI followed by a system reset or soft reset

You can program the watchdog timer via registers in the ISA I/O memory map. The watchdog timer is protected from being accidentally enabled and can support a range of count down time-outs up to eight minutes.

## **Memory Address Mapping**

Refer to Table 4-1 for memory address information.

| Address             | Size        | Description                    |  |

|---------------------|-------------|--------------------------------|--|

| FFF80000 - FFFFFFFF | 512K        | 512K BIOS PROM Area            |  |

| FEE01000 - FFF8FFFF | 18M-128K-4K | 18M-128K-4K PCI                |  |

| FEE00000 - FEE00FFF | 4K          | Local APIC Configuration Space |  |

| 40000000 - FEDFFFFF | 3G-18M      | PCI                            |  |

| 00100000 - 3FFFFFFF | 1023M       | Extended Memory                |  |

Table 4-1. Memory Addresses and Descriptions

| Address             | Size | Description                |  |

|---------------------|------|----------------------------|--|

| 000F0000 - 000FFFFF | 64K  | System BIOS Area           |  |

| 000E0000 - 000EFFFF | 64K  | Extended System BIOS Area  |  |

| 000C0000 - 000DFFFF | 128K | BIOS Option Expansion Area |  |

| 000A0000 - 000BFFFF | 128K | Video Buffer Area          |  |

| 00000000 - 0009FFFF | 640K | DOS Application Area       |  |

Table 4-1. Memory Addresses and Descriptions (Continued)

## I/O Address Map

Table 4-2 shows I/O addressing. You can use BIOS Setup or special utilities to enable or relocate these features from their default values.

| Address (hex)            | Size     | Description                           |  |

|--------------------------|----------|---------------------------------------|--|

| 0000 - 000F              | 16 bytes | PIIX4E DMA, channels 0 - 3            |  |

| 0020 - 0021              | 2 bytes  | PIIX4E Interrupt Controller 1         |  |

| 0040 - 0043              | 4 bytes  | PIIX4E - Timer 1                      |  |

| 0050 - 0057 <sup>1</sup> | 8 bytes  | LM78 Hardware Monitor                 |  |

| 0058 - 005F <sup>2</sup> | 8 bytes  | FPGA Functions (Watchdog Timer, ENUM) |  |

| 0060                     | 1 byte   | Keyboard Controller                   |  |

| 0061                     | 1 byte   | PIIX4E - NMI, Speaker Control         |  |

| 0064                     | 1 byte   | Keyboard Controller                   |  |

| 0070 - 7                 | 1 bit    | PIIX4E NMI Enable                     |  |

| 0070-6:0                 | 7 bits   | PIIX4E RTC                            |  |

| 0071                     | 1 byte   | PIIX4E RTC                            |  |

| 0072-0073                | 2 bytes  | PIIX4E RTC (extended registers)       |  |

| 0080 - 008F              | 16 bytes | PIIX4E DMA Page Register              |  |

| 0092                     | 1 byte   | PIIX4E Port 92 Register               |  |

| 00A0 - 00A1              | 2 bytes  | PIIX4E Interrupt Controller 2         |  |

| 00B2 - 00B3              | 2 bytes  | APM reserved                          |  |

Table 4-2. I/O Addresses and Descriptions

| Address (hex)     | Size     | Description                                  |  |  |

|-------------------|----------|----------------------------------------------|--|--|

| 00C0 - 00DE       | 31 bytes | PIIX4E DMA, channels 4 - 7                   |  |  |

| 00EA              | 1 byte   | Ultra I/O General Purpose I/O Index Register |  |  |

| 00EB              | 1 byte   | Ultra I/O General Purpose I/O Data Register  |  |  |

| 00F0              | 1 byte   | Reset Numeric Error                          |  |  |

| 0170 - 0177       | 8 bytes  | Secondary IDE Channel                        |  |  |

| 01F0 - 01F7       | 8 bytes  | Primary IDE Channel                          |  |  |

| 02F8 - 02FF       | 8 bytes  | COM2                                         |  |  |

| 0376              | 1 byte   | Secondary IDE Channel Command Port           |  |  |

| 0377              | 1 byte   | Secondary IDE Channel Status Port            |  |  |

| 0378 - 037F       | 8 bytes  | LPT1                                         |  |  |

| 03F0 <sup>3</sup> | 1 byte   | Ultra I/O Configuration Index Register       |  |  |

| 03F1 <sup>3</sup> | 1 byte   | Ultra I/O Configuration Data Register        |  |  |

| 03F0 - 03F5       | 6 bytes  | Floppy                                       |  |  |

| 03F6              | 1 byte   | Primary IDE Channel Command Port             |  |  |

| 03F7-7            | 1 bit    | Floppy Disk Change Channel 1                 |  |  |

| 03F7-6:0          | 7 bits   | Primary IDE Channel Status Port              |  |  |

| 03F7 (write)      | 1 byte   | Floppy Channel 1 Command                     |  |  |

| 03F8 - 03FF       | 8 bytes  | COM 1                                        |  |  |

| 04D0 - 04D1       | 2 bytes  | Interrupt Controller Edge/Level Register     |  |  |

| 0CF8 - 0CFB       | 4 bytes  | PCI CONFADD (DWORD Access Only)              |  |  |

| 0CFC - 0CFF       | 4 bytes  | PCI CONFDATA                                 |  |  |

| 0CF9              | 1 byte   | PIIX4E Reset Control Register                |  |  |

| FF00 - FF07       | 8 bytes  | IDE Bus Master Register                      |  |  |

#### Table 4-2. I/O Addresses and Descriptions (Continued)

| Address (hex)                                                                                                                                              | ex) Size Description                                   |                                           |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|--|--|--|--|--|

| FFA0 - FFA7                                                                                                                                                | 8 bytes                                                | Primary Bus Master IDE Registers          |  |  |  |  |  |

| FFA8 - FFAF                                                                                                                                                | FFA8 - FFAF 8 bytes Secondary Bus Master IDE Registers |                                           |  |  |  |  |  |

| FF80 - FF9F                                                                                                                                                | F80 - FF9F 32 bytes USB                                |                                           |  |  |  |  |  |

| <sup>1</sup> This address range is selected by Programmable Chip Select 1 (PCS0-) on the PIIX4E and is reprogrammable. PCS0- is initially set by the BIOS. |                                                        |                                           |  |  |  |  |  |

| -                                                                                                                                                          | •                                                      | Programmable Chip Select 2 (PCS1-) on the |  |  |  |  |  |

| Table 4-2. | I/O | Addresses a | Ind Desc | riptions | (Continued) |

|------------|-----|-------------|----------|----------|-------------|

|------------|-----|-------------|----------|----------|-------------|

PIIX4E and is reprogrammable. PCS1- is initially set by the BIOS.

<sup>3</sup> These registers are shared with the Floppy registers. Refer to the Ultra I/O data sheet via "Related Documentation" at the end of this manual.

## **Field Programmable Gate Array Registers**

The Field Programmable Gate Array (FPGA) is used for add-on features and control, and connects to the internal ISA bus. It consists of a group of I/O registers for control of features such as a Watchdog Timer, I/O switching control, NVRAM control and decoding, and system management functions. When a system management event occurs, the input causing the event latches and remains latched until cleared by the system software. The system management hardware notifies the system of the event depending on the mode selected by the user. Refer to Table 4-3.

| In:        | an:                                                                                                                                                                                        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Alarm Mode | alarm generates - You can connect the signal<br>to external alarm hardware. The front panel<br>alarm status indicator also illuminates when<br>an event occurs and alarm mode is selected. |

| IRQ Mode   | ISA interrupt generates - You can set the interrupt by writing to the IRQ select register.                                                                                                 |

| SCI Mode   | SCI generates - The FPGA's SCI output connects to the PIIX4 Therm input GPI8.                                                                                                              |

| NMI Mode   | NMI generates                                                                                                                                                                              |

Table 4-3. System Management Modes

### **FPGA Register Descriptions**

This section describes how to access the various FPGA register sets. The bit description tables below show bits 0 through 7 on the top line and bit functions on the second line.

You can access the FPGA registers by an index register at offset 05h from the base address of the FPGA (0x5Dh). The data register is located at offset 07h (0x5Fh). Refer to Table 4-4. To access an FPGA register, write to the index register first and then read/write from the data register. The BIOS sets the default FPGA Base address to 58h.

Table 4-4. Index and data register address and function

| Port                      | Offset address | Function                                          |  |  |

|---------------------------|----------------|---------------------------------------------------|--|--|

| Index                     | 05h            | Register Index Port - selects the device register |  |  |

| Data                      | 07h            | Data Port - read/write data to selected register  |  |  |

| Watchdog<br>Strobe/Status | 03h            | Watchdog Strobe and Status register               |  |  |

| DEVICE 00h<br>SYSTEM | DEVICE 10h<br>LAN A Ctrl | DEVICE 11h<br>LAN B Ctrl | DEVICE 14h<br>FLASH Ctrl | DEVICE 15h<br>SLOT Ctrl<br>Port |

|----------------------|--------------------------|--------------------------|--------------------------|---------------------------------|

| 00 Status            |                          |                          |                          |                                 |

|                      | 01 LAN A                 | 01 LAN B                 | 01 FLASH                 | 01 SLOT Ctrl                    |

| 02 EEPROM            |                          |                          |                          |                                 |

| 03 Watchdog          |                          |                          |                          |                                 |

| 04 INT Sel           |                          |                          |                          |                                 |

| 05 SCI Mask          |                          |                          |                          |                                 |

| 06 NMI Mask          |                          |                          |                          |                                 |

| 07 IRQ Mask          |                          |                          |                          |                                 |

| 08 Alm Mask          |                          |                          |                          |                                 |

| 09 FLT Latch         |                          |                          |                          |                                 |

| 0B Power On          |                          |                          |                          |                                 |

| OF DEV SEL           | 0F DEV SEL               | OF DEV SEL               | OF DEV SEL               | OF DEV SEL                      |

Refer to Table 4-5 for a map of the FPGA register set.

Table 4-5. Map of the FPGA register set

#### **Status Register**

The Status Register (STAT) is a read only register. Reads of the unused bits produce indeterminate values. Writes have no effect. The Temp Alarm, Fan Alarm, Alarm B, and Alarm A are all latched when active. You must initiate a write to index register 09 (Fault Latch) to clear the latched signals. Refer to Table 4-6.

Table 4-6. Bit descriptions for the STAT register

| 7 (most<br>significant<br>bit) | 6    | 5    | 4     | 3               | 2               | 1            | 0 (least<br>significant<br>bit) |

|--------------------------------|------|------|-------|-----------------|-----------------|--------------|---------------------------------|

| ALARM                          | FAL- | DEG- | ENUM- | LM78<br>ALARM A | LM78<br>ALARM B | SMB<br>ALERT | MMC2<br>TEMP<br>ALARM           |

#### MMC2 TEMP ALARM (Bit 0)

This signal connects to the MMC2's thermal sensor alarm output (ATF). You can program it to trip at a specific temperature. The input is latched when active (low). You can clear this bit (0) via Index register 09h. A read of these bits returns the latched status of the input.

#### SMB ALERT (Bit 1)

This bit reflects the level of the SMBus Alert signal.

#### LM78 ALARM A (Bit 3) and LM78 ALARM B (Bit 2)

The LM78 output functions feed these signals. The input is latched when active. You can clear these bits (3 and 2) via Index register 09h.

#### ENUM (Bit 4)

ENUM comes from the CPCI bus and signals the insertion of a new device. The input is latched when active (low). You can clear this bit (4) via Index register 09h. A read of this bit returns the latched status of the input.

#### DEG (Bit 5)

DEG comes from the CPCI bus and signals a power condition. The backplane may or may not support this ATX type signal.

#### FAL (Bit 6)

This signal comes from the CPCI bus and signals a power condition. The backplane may or may not support this ATX type signal.

#### ALARM (Bit 7)

This signal comes from device 0 Index Register 08h Alarm Enable.

#### **EEPROM Control Register**

The EEPROM Control Register (ECTRL) lets you access the external serial configuration EEPROM. Refer to Table 4-7.

Table 4-7. Bit descriptions for the ECTRL register

| 7 (most<br>significant<br>bit) | 6      | 5      | 4             | 3     | 2    | 1     | 0 (least<br>significant<br>bit) |

|--------------------------------|--------|--------|---------------|-------|------|-------|---------------------------------|

| Unused                         | Unused | Unused | EEPRG<br>Enbl | EERST | EEEN | EECLK | EEDTA                           |

Bits 0 through 4 are reserved for programming the FPGA's on card serial EEPROM.

#### Watchdog Timer Register

Refer to Table 4-8 for Watchdog Timer Register bit descriptions.

Table 4-8. Bit descriptions for the Watchdog Timer register

| 7 (most<br>significant<br>bit) | 6         | 5            | 4   | 3   | 2    | 1    | 0 (least<br>significant<br>bit) |

|--------------------------------|-----------|--------------|-----|-----|------|------|---------------------------------|

| CLR_STAT<br>US                 | ALARM_SET | SOFT<br>_RST | WD1 | WD0 | SEL2 | SEL1 | SEL0                            |

#### SEL0 (Bit 0), SEL1 (Bit 1) and SEL2 (Bit 2)

Use SEL0, SEL1 and SEL2 to select the watchdog timeout time. Writing to these bits does not clear or reset the watchdog timer. Refer to Table 4-9.

| Period                         | SEL2 | SEL1 | SEL0 |

|--------------------------------|------|------|------|

| .46 seconds                    | 0    | 0    | 0    |

| .93 seconds                    | 0    | 0    | 1    |

| 3.73seconds                    | 0    | 1    | 0    |

| 14.91 seconds                  | 0    | 1    | 1    |

| 29.8 seconds                   | 1    | 0    | 0    |

| 119 seconds,<br>(1.99 minutes) | 1    | 0    | 1    |

| 238 seconds,<br>(3.97 minutes) | 1    | 1    | 0    |

| 477 seconds,<br>(7.95 minutes) | 1    | 1    | 1    |

#### Table 4-9. Bit values for selecting watchdog timeout time

#### WD0 (Bit 3) and WD1 (Bit 4)

Use these bits to define the event that occurs on a watchdog timeout and to disable the watchdog timer. Reading these bits returns the last value written. Refer to Table 4-10.

| Name                                      | WD1 | WD0 | Description                                                                                                                              |

|-------------------------------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| DISABLED                                  | 0   | 0   | Resets watchdog. This mode disables the watchdog timer. No watchdog events occur.                                                        |

| POLLED                                    | 0   | 1   | This mode sets the watchdog into polled mode. The<br>Watchdog Strobe/Status port bit 2 polls for a<br>watchdog event.                    |

| FPGA IRQX                                 | 1   | 0   | This mode generates an IRQ on a watchdog<br>timeout. Refer to the Interrupt select register for<br>programming the particular interrupt. |

| NMI followed<br>by Reset or<br>Soft Reset | 1   | 1   | This mode first generates an NMI interrupt and<br>then a reset or soft reset.                                                            |

| Table 4-10. | Bit values | defining watchdog | g timeout and disabling |

|-------------|------------|-------------------|-------------------------|

|-------------|------------|-------------------|-------------------------|

#### SOFT\_RST (Bit 5)

Use this bit to change the Watchdog Reset function to Soft reset. Refer to Table 4-11. This bit clears on power-up reset.

Table 4-11. SOFT\_RST bit 5 settings

| Set bit to: | For:       |

|-------------|------------|

| 0 (default) | hard reset |

| 1           | soft reset |

#### ALARM\_SET (Bit 6)

Use this bit to force the FPGA Alarm to go active.

- □ Write a logic 1 to force an FPGA Alarm.

- □ Write a logic 0 to return the FPGA Alarm to its previous state (active if watchdog or EXT\_ALARM are active).

- **□** Read this bit to return the last written value.

#### CLR\_STATUS (Bit 7)

Use this bit to reset and enable the watchdog timer FPGA ALARM output latch.

- □ Write a logic 1 to hold the watchdog timer FPGA ALARM output latch in a reset state.

- □ Write a logic 0 to allow the watchdog timer FPGA ALARM output latch to latch a watchdog timeout.

Strobe the watchdog timer before enabling the latch to make sure that a watchdog timeout did not occur before the latch enabled.

Reading this bit returns the last written value.

#### Interrupt Select Register

Use the Interrupt Select Register to select the desired IRQ line. Refer to Table 4-12. This IRQ can then be generated by a watchdog Timeout or ENUM-.

| Table 4-12. | . Bit descriptions for the INT | UM register |

|-------------|--------------------------------|-------------|

|-------------|--------------------------------|-------------|

| 7 (most<br>significant<br>bit) | 6      | 5      | 4      | 3       | 2       | 1       | 0 (least<br>significant<br>bit) |

|--------------------------------|--------|--------|--------|---------|---------|---------|---------------------------------|

| Unused                         | Unused | Unused | Unused | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0                         |

4

## IRQSEL0 (Bit 0), IRQSEL1 (Bit 1), IRQSEL2 (Bit 2) and IRQSEL3 (Bit 3)

These bits determine which IRQ is driven when an IRQ even triggers. Refer to Table 4-13.

| Interrupt Line  | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 |

|-----------------|---------|---------|---------|---------|

| No IRQ Selected | 0       | 0       | 0       | 0       |

| No IRQ Selected | 0       | 0       | 0       | 1       |

| No IRQ Selected | 0       | 0       | 1       | 0       |

| No IRQ Selected | 0       | 0       | 1       | 1       |

| No IRQ Selected | 0       | 1       | 0       | 0       |

| Select IRQ5     | 0       | 1       | 0       | 1       |

| No IRQ Selected | 0       | 1       | 1       | 0       |

| Select IRQ7     | 0       | 1       | 1       | 1       |

| No IRQ Selected | 1       | 0       | 0       | 0       |

| Select IRQ9     | 1       | 0       | 0       | 1       |

| Select IRQ10    | 1       | 0       | 1       | 0       |

| Select IRQ11    | 1       | 0       | 1       | 1       |

| No IRQ Selected | 1       | 1       | 0       | 0       |

| No IRQ Selected | 1       | 1       | 0       | 1       |

| No IRQ Selected | 1       | 1       | 1       | 0       |

| No IRQ Selected | 1       | 1       | 1       | 1       |

Table 4-13. Bit values for determining driven IRQ lines

#### **SCI Enable Register**

The SCI Enable Register (SCIEN) defines the type of events that can generate an SCI. Refer to Table 4-14.

Table 4-14. Bit descriptions for the SCIEN register

| 7 (most<br>significant<br>bit) | 6      | 5      | 4     | 3        | 2        | 1     | 0 (least<br>significant<br>bit) |

|--------------------------------|--------|--------|-------|----------|----------|-------|---------------------------------|

| ENABLE                         | Unused | Unused | ENUM- | ALARM_A- | ALARM_B- | TEMP- | SMB_ALE<br>RT-                  |

#### SMB\_ALERT (Bit 0)

- □ Set to a logic 1 to allow generation of an SCI when SMB ALERT is active. SMB ALERT is active when logic 0.

- □ Write a logic 0 to this bit to disable an SCI for this event.

#### TEMP (Bit 1)

- □ Set to a logic 1 to allow generation of an SCI when TEMP is active. TEMP is the ATF signal from the MMC2 and is active when logic 0.

- □ Write a logic 0 to this bit to disable an SCI for this event.

#### ALARM\_A (Bit 3) and ALARM\_B (Bit 2)

- □ Set to a logic 1 to allow the generation of an SCI when the ALARM\_A or ALARM\_B go active. Alarm is active when logic 0.

- □ Write a logic 0 to these bits to disable an SCI for this event.

#### ENUM (Bit 4)

- □ Set to a logic 1 to allow generation of an SCI when the ENUM event occurs.

- □ Write a logic 0 to this bit to disable an SCI for this event.

#### ENABLE

- □ Set to a logic 1 to allow generation of an SCI by one of the events above.

- $\Box$  Write a logic 0 to prevent the events from generating an SCI.

#### NMI Enable Register

4

The NMI Enable Register (NMIEN) defines the events that can generate an NMI. Refer to Table 4-15.

#### Table 4-15. Bit descriptions for the NMIEN register

| 7 (most<br>significant<br>bit) | 6      | 5      | 4    | 3       | 2       | 1    | 0 (least<br>significant<br>bit) |

|--------------------------------|--------|--------|------|---------|---------|------|---------------------------------|